- 您现在的位置:买卖IC网 > Sheet目录342 > MCBSTM32EXL (Keil)BOARD EVALUATION FOR STM32F103ZE

Inter-integrated circuit (I 2 C) interface

RM0008

Closing the communication

After writing the last byte to the DR register, the STOP bit is set by software to generate a

Stop condition (see Figure 235 Transfer sequencing EV8_2). The interface goes

automatically back to slave mode (M/SL bit cleared).

Note:

Stop condition should be programmed during EV8_2 event, when either TxE or BTF is set.

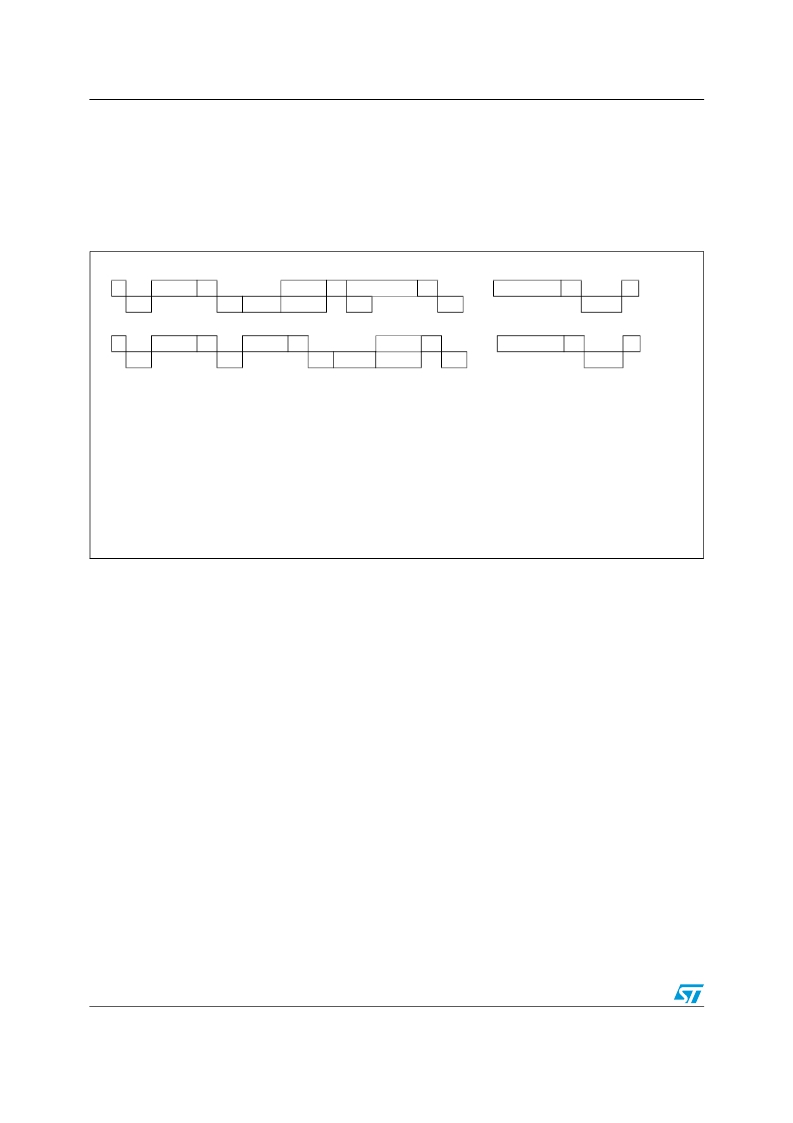

Figure 235. Transfer sequence diagram for master transmitter

Master receiver

Following the address transmission and after clearing ADDR, the I 2 C interface enters

Master Receiver mode. In this mode the interface receives bytes from the SDA line into the

DR register via the internal shift register. After each byte the interface generates in

sequence:

●

●

An acknowledge pulse if the ACK bit is set

The RxNE bit is set and an interrupt is generated if the ITEVFEN and ITBUFEN bits are

set (see Figure 236 Transfer sequencing EV7).

If the RxNE bit is set and the data in the DR register is not read before the end of the last

data reception, the BTF bit is set by hardware and the interface waits until BTF is cleared by

a read in the SR1 register followed by a read in the DR register, stretching SCL low.

632/995

Doc ID 13902 Rev 9

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

MCBTMPM330

BOARD EVAL TOSHIBA TMPM330 SER

MCIMX25WPDKJ

KIT DEVELOPMENT WINCE IMX25

MCIMX53-START-R

KIT DEVELOPMENT I.MX53

MCM69C432TQ20

IC CAM 1MB 50MHZ 100LQFP

MCP1401T-E/OT

IC MOSFET DRVR INV 500MA SOT23-5

MCP1403T-E/MF

IC MOSFET DRIVER 4.5A DUAL 8DFN

MCP1406-E/SN

IC MOSFET DVR 6A 8SOIC

MCP14628T-E/MF

IC MOSFET DVR 2A SYNC BUCK 8-DFN

相关代理商/技术参数

MCBSTM32EXLU

功能描述:开发板和工具包 - ARM EVAL BOARD + ULINK2 FOR STM32F103ZG

RoHS:否 制造商:Arduino 产品:Development Boards 工具用于评估:ATSAM3X8EA-AU 核心:ARM Cortex M3 接口类型:DAC, ICSP, JTAG, UART, USB 工作电源电压:3.3 V

MCBSTM32EXLU-ED

制造商:ARM Ltd 功能描述:KEIL STM STM32EXL EVAL BOARD

MCBSTM32EXLUME

功能描述:开发板和工具包 - ARM EVAL BOARD + ULINKME FOR STM32F103ZG

RoHS:否 制造商:Arduino 产品:Development Boards 工具用于评估:ATSAM3X8EA-AU 核心:ARM Cortex M3 接口类型:DAC, ICSP, JTAG, UART, USB 工作电源电压:3.3 V

MCBSTM32F200

功能描述:开发板和工具包 - ARM EVAL BOARD FOR STM STM32F207IG

RoHS:否 制造商:Arduino 产品:Development Boards 工具用于评估:ATSAM3X8EA-AU 核心:ARM Cortex M3 接口类型:DAC, ICSP, JTAG, UART, USB 工作电源电压:3.3 V

MCBSTM32F200U

功能描述:开发板和工具包 - ARM EVAL BOARD FOR STM STM32F207IG + ULINK2

RoHS:否 制造商:Arduino 产品:Development Boards 工具用于评估:ATSAM3X8EA-AU 核心:ARM Cortex M3 接口类型:DAC, ICSP, JTAG, UART, USB 工作电源电压:3.3 V

MCBSTM32F200UME

功能描述:开发板和工具包 - ARM EVAL BOARD FOR STM STM32F207IG ULINK-ME

RoHS:否 制造商:Arduino 产品:Development Boards 工具用于评估:ATSAM3X8EA-AU 核心:ARM Cortex M3 接口类型:DAC, ICSP, JTAG, UART, USB 工作电源电压:3.3 V

MCBSTM32F200UME-ED

制造商:ARM Ltd 功能描述:KEIL STM32F207IG EVAL BOARD

MCBSTM32F400

功能描述:开发板和工具包 - ARM EVAL BOARD FOR STM STM32F407IG

RoHS:否 制造商:Arduino 产品:Development Boards 工具用于评估:ATSAM3X8EA-AU 核心:ARM Cortex M3 接口类型:DAC, ICSP, JTAG, UART, USB 工作电源电压:3.3 V